PCI Express

PCI Express (Peripheral Component Interconnect Express, lyhennettynä PCIe) on suurinopeuksinen tietokoneen standardoitu väylätyyppi, joka on suunniteltu korvaamaan vanhemmat PCI, PCI-X ja AGP-liitäntästandardit. PCIe-liitäntä sisältää useita parannuksia edeltäjiinsä nähden, joita ovat muun muassa suurempi siirtokyky, siirtyminen sarjamuotoiseen tiedonsiirtoon rinnakkaisesta, väylän parempi skaalattavuus, sekä pienempi siirräntäpinnien määrä, jonka ansiosta PCIe-liittimillä on pienempi fyysinen tilantarve. PCIe:ssä on myös yksityiskohtaisempi virheiden havaitsemis- ja raportointimekanismi (Advanced Error Reporting (AER)[1]) ja lisäksi sen viimeisimmät versiot tukevat I/O-virtualisointia.[1] PCIe on vähitellen korvannut edeltäjänsä (AGP, PCI ja PCI-X), ja on tämän seurauksena noussut hallitsevaksi väylätyypiksi pöytätietokoneissa.[2][3] PCIe:n sähköteknisiä puolia on hyödynnetty useissa siihen pohjautuvissa muunnelmissa, joista ehkä huomattavimpana voidaan mainita ExpressCard, PCIe:n kannettaville tietokoneille suunniteltu versio.

PCIe-liitäntästandardia ylläpitää PCI-SIG (PCI Special Interest Group), johon kuuluu yli 900 tietotekniikka-alan yritystä. Maaliskuussa 2015 viimeisin tuotannossa ja kuluttajamarkkinoilla saatavilla oleva PCIe-versio oli 3.1.[4]

Muutokset entiseen

[muokkaa | muokkaa wikitekstiä]PCIe poikkeaa arkkitehtuuriltaan huomattavasti aikaisemmista väylistä, ja tästä syystä se poikkeaa täysin myös PCI-väylästä. Yleensä väylä koostuu yhteisestä tiedonsiirtokanavasta, johon kaikki väylään kytketyt laitteet liittyvät, ja jota laitteet käyttävät vuorotellen. PCIe taas muistuttaa pakettikytkentäistä tiedonsiirtoverkkoa (erityisesti Ethernetin nykyaikaista tähtimäistä versiota) OSI-mallin mukaisella protokollapinolla, joten periaatteessa PCIe ei ole väylä sanan perinteisessä merkityksessä. PCIe:ssä jokaisella laitteella on oma tiedonsiirtokanava kytkimeen. Tiedonsiirtokanava koostuu linjoista (engl. lane). Yksi linja koostuu kahdesta yksisuuntaisesta johdinparista, joista toinen siirtää tietoa kytkimen suuntaan ja toinen taas kytkimeltä laitteelle. Tämän ansiosta voidaan samanaikaisesti siirtää tietoa molempiin suuntiin. Standardi tukee 1, 2, 4, 8, 12, 16 ja 32 linjan ratkaisuja, joista nykyään yleisimmin käytössä ovat yhden (×1), neljän (×4), kahdeksan (×8) ja 16 (×16) linjan kytkennät.[5] Kytkin reitittää tietoa PCIe -laitteiden ja muun järjestelmän välillä tiedonsiirtopakettien otsikkokenttien sisältämän tiedon perusteella.[3] Toisin kuin monet aiemmat väylätekniikat, PCIe käyttää CRC-summaa luotettavuuden parantamiseksi.[6]

PCIe:tä käytetään myös keskeisenä osana IBM PC -yhteensopivien tietokoneiden arkkitehtuuria. Suorittimelta tulee parikymmentä PCIe-linjaa (lane). Tyypillisesti 16 menee suoraan näytönohjaimelle, joka on ensimmäisessä PCIe-korttipaikassa, neljä menee piirisarjalle, jossa ovat mm. SATA- ja USB-ohjaimet. Toinen tärkeä käyttötarkoitus on M.2-liittimeen kytkettävät nopeat SSD-levyt. M.2 käyttää maksimissaan neljä linjaa. Lisäksi emolevyn piirisarja saattaa tarjota lisää linjaa käytettäväksi omasta kaistastaan esim. PCIe-korttipaikoille ja M.2-liittimille.[7][8][9][10]

PCIe-tyypit ja -muunnokset

[muokkaa | muokkaa wikitekstiä]| Tähän artikkeliin tai osioon ei ole merkitty lähteitä, joten tiedot kannattaa tarkistaa muista tietolähteistä. Voit auttaa Wikipediaa lisäämällä artikkeliin tarkistettavissa olevia lähteitä ja merkitsemällä ne ohjeen mukaan. |

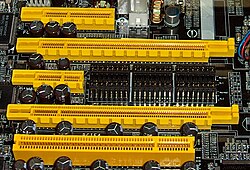

Täysikokoinen PCI Express

[muokkaa | muokkaa wikitekstiä]

- PCI Express ×4

- PCI Express ×16

- PCI Express ×1

- PCI Express ×16

- PCI (32-bittinen)

Täysikokoisia PCIe kortteja käytetään etenkin pöytätietokoneissa. Kortit sopivat kantansa kokoiseen tai suurempaan PCIe-paikkaan, mutta eivät useimmissa tapauksissa pienempään ilman modifiointia. On tosin myös saatavilla emolevyjä, joissa PCIe-porttien toinen pää on avoin mahdollistaen pidempien korttien asentamisen pienempään liittimeen. Joissain emolevyissä on jätetty myös osa liitännöistä asentamatta, vaikka liittimen fyysinen koko olisi mahdollistanut niiden käytön.[5] PCI Express -liittimien pituuserot johtuvat niiden vaihtelevasta pinnimäärästä. Lyhemmissä liittimissä on vähemmän pinnejä, ja ne pystyvät tämän takia pienempiin siirtonopeuksiin, mutta vaativat kuitenkin samalla vähemmän tilaa emolevyllä. Pidempien liitinten etuna on niiden tarjoama suurempi siirtonopeus, mutta ne vaativat vastaavasti enemmän tilaa emolevyllä.

Tästä esimerkkinä ×16-paikka, joka toimii ×4 nopeuksilla. Korttipaikkaan mahtuu mikä tahansa ×1, ×2, ×4, ×8 tai ×16 -kortti, mutta se antaa kortille vain ×4-nopeuden. Tällainen konfiguraatio voidaan ilmoittaa esimerkiksi seuraavilla tavoilla: ×16 (×4 mode); tai "×koko @ ×nopeudella" (×16 @ ×4). Tällaisten liittimien etuna on niiden tuoma mahdollisuus asentaa suurempia kortteja ilman, että emolevyn tarvitsee tukea kortin vaatimaa täyttä nopeutta.

Kytkennät

[muokkaa | muokkaa wikitekstiä]Seuraavassa taulukossa esitetään PCI Express kortin A- ja B-puolien nastojen käyttötarkoitukset.

| Nasta | B-puoli | A-puoli | Käyttötarkoitus | Nasta | B-puoli | A-puoli | Käyttötarkoitus | |

|---|---|---|---|---|---|---|---|---|

| 1 | +12 V | PRSNT1# | Kytketään kauimmaiseen PRSNT2# nastaan | 50 | HSOp(8) | Varattu | Linja 8 datan lähetys, + ja − | |

| 2 | +12 V | +12 V | 51 | HSOn(8) | Maa | |||

| 3 | +12 V | +12 V | 52 | Maa | HSIp(8) | Linja 8 datan vastaanotto, + ja - | ||

| 4 | Maa | Maa | 53 | Maa | HSIn(8) | |||

| 5 | SMCLK | TCK | SMBus ja JTAG port pins | 54 | HSOp(9) | Maa | Linja 9 datan lähetys, + ja − | |

| 6 | SMDAT | TDI | 55 | HSOn(9) | Maa | |||

| 7 | Maa | TDO | 56 | Maa | HSIp(9) | Linja 9 datan vastaanotto, + ja - | ||

| 8 | +3.3 V | TMS | 57 | Maa | HSIn(9) | |||

| 9 | TRST# | +3.3 V | 58 | HSOp(10) | Maa | Linja 10 datan lähetys, + ja − | ||

| 10 | +3.3 V aux | +3.3 V | Standby power | 59 | HSOn(10) | Maa | ||

| 11 | WAKE# | PERST# | Link reactivation; fundamental reset | 60 | Maa | HSIp(10) | Linja 10 datan vastaanotto, + ja - | |

| Key notch | 61 | Maa | HSIn(10) | |||||

| 12 | CLKREQ# | Maa | Request running clock | 62 | HSOp(11) | Maa | Linja 11 datan lähetys, + ja − | |

| 13 | Maa | REFCLK+ | Reference clock differential pair | 63 | HSOn(11) | Maa | ||

| 14 | HSOp(0) | REFCLK− | Linja 0 datan lähetys, + ja − | 64 | Maa | HSIp(11) | Linja 11 datan vastaanotto, + ja - | |

| 15 | HSOn(0) | Maa | 65 | Maa | HSIn(11) | |||

| 16 | Maa | HSIp(0) | Linja 0 datan vastaanotto, + ja − | 66 | HSOp(12) | Maa | Linja 12 datan lähetys, + ja − | |

| 17 | PRSNT2# | HSIn(0) | 67 | HSOn(12) | Maa | |||

| 18 | Maa | Maa | 68 | Maa | HSIp(12) | Linja 12 datan vastaanotto, + ja - | ||

| PCI Express ×1 cards end at pin 18 | 69 | Maa | HSIn(12) | |||||

| 19 | HSOp(1) | Varattu | Linja 1 datan lähetys, + ja − | 70 | HSOp(13) | Maa | Linja 13 datan lähetys, + ja − | |

| 20 | HSOn(1) | Maa | 71 | HSOn(13) | Maa | |||

| 21 | Maa | HSIp(1) | Linja 1 datan vastaanotto, + ja − | 72 | Maa | HSIp(13) | Linja 13 datan vastaanotto, + ja − | |

| 22 | Maa | HSIn(1) | 73 | Maa | HSIn(13) | |||

| 23 | HSOp(2) | Maa | Linja 2 datan lähetys, + ja − | 74 | HSOp(14) | Maa | Linja 14 datan lähetys, + ja − | |

| 24 | HSOn(2) | Maa | 75 | HSOn(14) | Maa | |||

| 25 | Maa | HSIp(2) | Linja 2 datan vastaanotto, + ja − | 76 | Maa | HSIp(14) | Linja 14 datan vastaanotto, + ja − | |

| 26 | Maa | HSIn(2) | 77 | Maa | HSIn(14) | |||

| 27 | HSOp(3) | Maa | Linja 3 datan lähetys, + ja − | 78 | HSOp(15) | Maa | Linja 15 datan lähetys, + ja − | |

| 28 | HSOn(3) | Maa | 79 | HSOn(15) | Maa | |||

| 29 | Maa | HSIp(3) | Linja 3 datan vastaanotto, + ja − | 80 | Maa | HSIp(15) | Linja 15 datan vastaanotto, + ja − | |

| 30 | Varattu | HSIn(3) | 81 | PRSNT2# | HSIn(15) | |||

| 31 | PRSNT2# | Maa | 82 | Varattu | Maa | |||

| 32 | Maa | Varattu | ||||||

| PCI Express ×4 cards end at pin 32 | ||||||||

| 33 | HSOp(4) | Varattu | Linja 4 datan lähetys, + ja − | |||||

| 34 | HSOn(4) | Naa | ||||||

| 35 | Maa | HSIp(4) | Linja 4 datan vastaanotto, + ja − | |||||

| 36 | Maa | HSIn(4) | ||||||

| 37 | HSOp(5) | Maa | Linja 5 datan lähetys, + ja − | |||||

| 38 | HSOn(5) | Maa | ||||||

| 39 | Maa | HSIp(5) | Linja 5 datan vastaanotto, + ja − | |||||

| 40 | Maa | HSIn(5) | ||||||

| 41 | HSOp(6) | Maa | Linja 6 datan lähetys, + ja − | |||||

| 42 | HSOn(6) | Maa | ||||||

| 43 | Maa | HSIp(6) | Linja 6 datan vastaanotto, + ja − | Selitykset | ||||

| 44 | Maa | HSIn(6) | Maa (GND) | 0 V (maa) | ||||

| 45 | HSOp(7) | Maa | Linja 7 datan lähetysja, + ja − | Virta | PCIe-kortin virransyöttö | |||

| 46 | HSOn(7) | Maa | Output-nasta | Signaalit kortista emolevylle | ||||

| 47 | Maa | HSIp(7) | Linja 7 datan vastaanotto, + ja − | Input-nasta | Signaalit emolevystä kortille | |||

| 48 | PRSNT2# | HSIn(7) | Open drain | May be pulled low or sensed by multiple cards | ||||

| 49 | Maa | Maa | Sense-nasta | Tied together on card | ||||

| PCI Express ×8 cards end at pin 49 | Varattu | Ei käytössä | ||||||

PCI Express Mini -kortti

[muokkaa | muokkaa wikitekstiä]

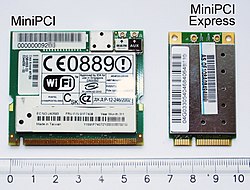

PCI Express Mini Card (myös Mini PCI Express, Mini PCIe, Mini PCI-E, mPCIe tai PEM) on PCI Express -väylään pohjautuva korvaaja vanhemmalle Mini PCI -liitännälle. Sen on kehittänyt PCI-SIG, ja liitäntä tukee sekä PCIe- että USB 2.0 -toiminnallisuuksia. Monet vuoden 2005 jälkeen valmistetut kannettavat tietokoneet tukevat jotain PCIe-pohjaista liitäntästandardia.[11]

Fyysiset mitat

[muokkaa | muokkaa wikitekstiä]PCI Express Mini -kortin ulkomitat ovat 30×50,95 mm. Kytkentä kortin ja emolevyn välillä tapahtuu 52-pinnisellä liittimellä, jonka pinnit on jaettu kahdelle puolelle. Yhden pinnin leveys on 0,6 mm. Kummallakin puolella on 26 pinniä, jotka on jaettu yhteen kahdeksan ja yhteen 18 pinnin osaan. (katso kuva) Mini-kortista on olemassa myös puolet pienempi versio, jonka ulkomitat ovat 30×26,8 mm. mPCIe piirilevyn paksuus on 1,0 mm ilman komponentteja.[11]

PCIe-liitännän muunnoksia

[muokkaa | muokkaa wikitekstiä]Monet muut laajennuskortit on kehitetty PCIe:n pohjalta. Näihin kuuluvat muun muassa:

- ExpressCard[12]

- PCI Express ExpressModule

- XQD card

- XMC

- AdvancedTCA

- AMC

- FeaturePak

- Universal IO

- Thunderbolt

- Serial Digital Video Out

- M.2 (tunnettu myös nimellä NGFF)

- M-PCIe PCIe 3.0 mobiililaitteille, kuten älypuhelimille ja tableteille.[13][14]

Historia ja versiot

[muokkaa | muokkaa wikitekstiä]PCIe-liitännän suunnitteluvaiheessa sitä kutsuttiin lyhenteellä HSI (for High Speed Interconnect), joka vaihtui vielä nimelle 3GIO (for 3rd Generation I/O) ennen lopullista asettumistaan PCI Express nimelle, jolla liitäntä nykyisin tunnetaan. Työ PCIe-standardin kanssa käynnisyi Arapaho Work Group (AWG) -ryhmässä, joka koostui alkuun vain Intelin insinööreistä. Myöhemmin siihen liittyi kuitenkin henkilöitä Intelin kanssa yhteistyötä tehneistä yrityksistä.[15]

PCIe -tekniikkaa päivitetään edelleen.

| PCI Express versio |

Koodaus | Linjaa kohti (×1) | ×16 -liittimestä (16 linjaa) | ||||

|---|---|---|---|---|---|---|---|

| Raakabittinopeus[a][b] | Kaistanleveys[a] | Raakabittinopeus[a][b] | Kaistanleveys[a] | ||||

| 1.0 | NRZ | 8b/10b | 2,5 GT/s | 2 Gbit/s | 250 MB/s | 40 GT/s | 4 GB/s |

| 2.0 | 8b/10b | 5 GT/s | 4 Gbit/s | 500 MB/s | 80 GT/s | 8 GB/s | |

| 3.0 | 128b/130b | 8 GT/s | 7,877 Gbit/s | 984,6 MB/s | 128 GT/s | 15,754 GB/s | |

| 4.0 | 128b/130b | 16 GT/s | 15,754 Gbit/s | 1969,2 MB/s | 256 GT/s | 31,508 GB/s | |

| 5.0 | 128b/130b | 32 GT/s | |||||

| 6.0 | PAM4[18] | FLIT[18] | 64 GT/s | ||||

| 7.0 | |||||||

PCI Express 1.0a

[muokkaa | muokkaa wikitekstiä]PCI-SIG esitteli 2003 PCIe 1.0a -liitännän, joka pystyi siirtämään 250 MB/s dataa linjaa kohden ja saavuttamaan 2,5 GT/s siirtonopeuden.[19] GT viittaa "gigasiirtoihin" (ei gigatavuihin) sekunnissa, joka liittyy väylässä käytettyyn tiedon koodaustapaan.[19] 8b/10b-koodausmenetelmällä kahdeksan bittiä on koodattu 10-bittisellä symbolilla, joka puretaan vastaanottajassa.[19] Väylän on siis siirrettävä 10 bittiä kahdeksan databitin siirtoon.[19]

PCIe-väylä on kaksisuuntainen: siirrettäessä 2.5 Gbps (gigabittiä sekunnissa) kokonaissiirtonopeus on 5 Gbps.[19] Enkoodauksen myötä käytännön siirtonopeus on tällöin 4 Gbps.[19] Väylässä voi olla useita linjoja moninkertaistaen siirtonopeuden: 16 linjan PCIe 1.1 -väylä voi siirtää 80 Gbps koodattua tietoa tai 64 Gbps koodaamatonta tietoa.[19] Linkki toimii 2,5 GHz kellotaajuudella kuljettaen 250 000 000 tehollista tavua sekunnissa yhtä linjaa kohden (250 MB/s) suurimmalla nopeudellaan.[5][19]

PCI Express 1.1

[muokkaa | muokkaa wikitekstiä]PCI-SIG julkaisi helmikuussa 2005 PCIe 1.1 -liitännän.[20] Päivitys sisälsi useita täsmennyksiä ja parannuksia, mutta se oli täysin yhteensopiva edellisen PCIe 1.0a -standardin kanssa. Päivitys ei sisältänyt muutoksia tiedonsiirtonopeuksiin.

PCI Express 2.0

[muokkaa | muokkaa wikitekstiä]PCI-SIG julkaisi PCI Express Base 2.0 -määritelmän 15. tammikuuta 2007.[21] PCIe 2.0 -standardissa on kaksinkertaiset tiedonsiirtonopeudet 1.0 -standardiin nähden (2,5 GT/s vs 5 GT/s; 250 MB/s vs 500 MB/s). 32-kaistainen PCIe-liitäntä (×32) pystyy siirtämään yhteenlaskettuna 16 GB/s.

PCIe 2.0 -emolevyliitännät ovat täysin yhteensopivia PCIe v1.x -korttien kanssa. PCIe 2.0 toimivat myös PCIe 1.x liitännässä, mutta niiden PCI Express 1.1 -standardin mukainen pienempi kaistanleveys rajoittaa niiden toimintaa. Yleisesti ottaen PCIe 2.0 -liitännälle suunnitellut näytönohjaimet toimivat v1.1 tai v1.0a emolevyjen kanssa ja päinvastoin.

The PCI-SIG kertoi myös, että PCIe 2.0 sisältää parannuksia Point-to-Point -siirtoprotokollaan ja ohjelmistoarkkitehtuuriin.[22]

Intelin ensimmäinen PCIe 2.0 yhteensopiva piirisarja oli X38, ja ensimmäisten siihen pohjautuvien emolevyjen toimitukset alkoivat eri valmistajilta (Abit, Asus, Gigabyte) lokakuussa 2007.[23] AMD alkoi tukea PCIe 2.0:aa AMD 700 -piirisarjasta ja NVIDIA MCP72 -piirisarjasta.[24] Kaikki Intelin edelliset piirisarjat, mukaan lukien Intel P35 tukivat PCIe 1.1 tai 1.0a -standardia.[25]

PCIe 2.0 käyttää 1.x -liitännän tapaan 8b/10b-koodausta[5], toimittaen tehollisen 4 Gbit/s siirtonopeuden per kaista.

PCI Express 2.1

[muokkaa | muokkaa wikitekstiä]PCI Express 2.1 tukee suurta osaa PCIe 3.0:lle suunnitelluista käsittely-, tuki- ja ongelmanratkaisupäivityksistä. Sen siirtonopeudet ovat tosin samat, kuin PCIe 2.0 -liitännässä, mutta osa 2.1-standardille suunnitelluista korteista ei ole yhteensopivia joidenkin vanhempien 1.0 tai 1.0a -emolevyjen kanssa, koska 2.1-standardin kortit ottavat enemmän tehoa PCIe-liitännästä.[26] Useille 1.1-standardin emolevyille on saatavilla BIOS-päivitys, joka tekee niistä yhteensopivia 2.1-korttien kanssa.

PCI Express 3.x

[muokkaa | muokkaa wikitekstiä]| Tätä artikkelia tai sen osaa on pyydetty päivitettäväksi, koska sen sisältö on osin vanhentunut. Voit auttaa Wikipediaa parantamalla artikkelia. Lisää tietoa saattaa olla keskustelusivulla. Tarkennus: Versio 3.0:n tiedot eivät ole ajantasalla. |

PCI Express 3.0 tuli saataville marraskuussa 2010 useiden viivästymisten jälkeen. Tätä ennen elokuussa 2007, PCI-SIG oli ilmoittanut, että tuleva PCI Express 3.0 pystyisi 8 GT/s siirtonopeuksiin, mutta olisi silti samalla taaksepäin yhteensopiva edellisten PCIe-versioiden kanssa. Samalla ilmoitettiin, että PCI Express 3.0 lopullinen määritelmä tulisi viivästymään vuodelle 2011.[27][28]

Kuuden kuukauden tutkimusten jälkeen PCI-SIG totesi 8 GT/s siirtonopeuksien toteuttamisen mahdolliseksi jo olemassa olevalla edullisilla materiaaleilla, tekniikalla ja infrastruktuurilla ilman, että menetetään yhteensopivuus PCIe-protokollapinoon (PCIe protocol stack).

PCIe 3.0 -standardissa siirrytään edellisissä versioissa käytetystä 8b/10b-koodauksesta 128b/130b-koodaukseen.[17][5]

18. marraskuuta 2010 PCI Special Interest Group julkaisi lopullisen PCI Express 3.0 -standardin.[29]

PCI Express 3.1 suunniteltiin julkaistavaksi vuoden 2013 lopulla tai 2014 alussa.[14][30]

Siirtonopeuksien lisäksi kehityskohteita ovat olleet tuki IO:n virtualisoinnille ja laitteen jakamiselle useiden virtuaalikoneiden kanssa.[31] Lisäksi vihjeitä välimuistin käytölle, atomisille toiminnoille ja alhaisen latenssin pääsy ovat olleet kehityskohteina.[31] Myös alhaisemman virran tiloja on kehitetty kädessä pidettäviä laitteita varten.[31]

PCI Express 4.0

[muokkaa | muokkaa wikitekstiä]PCI-SIG julkaisi 29. marraskuuta 2011 PCI Express 4.0 -standardin, joka pystyy 16 GT/s siirtonopeuksiin kuparipohjaisella tekniikalla.[32][33] 4.0:n lopullinen julkaisu on PCI-SIGin mukaan vuoden 2016 loppupuolella.[34] Määrittely julkaistiin virallisesti 8. kesäkuuta 2017.[35]

Liitäntä käyttää PCIe 3.0:n tapaan 128b/130b-koodausta ja on edeltäjiensä tapaan yhteensopiva edellisten PCIe-sukupolvien kanssa.[5][36]

PCI Express 5.0

[muokkaa | muokkaa wikitekstiä]17. tammikuuta 2019 PCI-SIG ilmoitti ratifioineensa version 0.9 PCI Express 5.0 -määrittelystä.[37] Muutos 4.0:sta 5.0:aan koski pääasiassa nopeuden kasvattamista.[31] 5.0:ssa tuli myös sisäänrakennettu tuki vaihtoehtoisille protokollille.[31]

PCI Express 6.0

[muokkaa | muokkaa wikitekstiä]18. kesäkuuta 2019 PCI-SIG ilmoitti PCIe 6.0 -määrittelyn tulevan vuonna 2021.[38] 6.0 versiossa signaalin enkoodaus muuttuu aiemmin käytetystä.[39] PCIe 6.0 määrittely on julkaistu tammikuussa 2022.[40]

Versiossa 6.0 aiemmin käytetyn NRZ (Non-Return-to-Zero) -tekniikan sijaan käytössä on PAM4 (Pulse-Amplitude Modulation 4). Kahden signaalitason (korkea/matala) sijaan PAM4 käyttää neljää signaalitasoa, jolloin signaali voi koodata neljä bittijaksoa: 00, 01, 10, 11. Tämän myötä PAM4 voi siirtää kaksi kertaa enemmän tietoa kuin NRZ ilman tarvetta kaistanleveyden kasvattamiselle.[18]

PAM4-koodauksen haittana NRZ-koodaukseen verrattuna ovat korkeampi kustannus ja signaali on herkempi häiriöille, josta johtuen standardissa on mukana Forward Error Correction (FEC) virheenkorjausmekanismi. FEC lisää virheenkorjauskoodin jatkuvana virtana, jonka tarkoitus on varmistaa kriittistä tietoa kun uudelleen lähetykseen ei ole aikaa. FEC:n lisäksi käytössä CRC-summa viimeisenä tarkastuksena, jonka epäonnistuessa data on pakko lähettää uudelleen.[18]

PAM4:n ja FEC:n lisäksi PCIe 6.0:ssa on FLIT-koodaus (FLow control unIT). PAM4 on fyysisen kerroksen koodaus ja FLIT-koodausta käytetään loogisella tasolla datan pilkkomiseen kiinteän kokoisiin paketteihin. Kiinteän kokoiset paketit tarvitaan FEC:n ja virheenkorjauksen vuoksi.[18]

PCI Express 7.0

[muokkaa | muokkaa wikitekstiä]PCI-SIG on tehnyt hahmotelman versiosta 7.0, jonka se aikoo viimeistellä vuoteen 2025 mennessä.[41]

Yhteensopivuus

[muokkaa | muokkaa wikitekstiä]PCIe -liittimiä on standardoitu muun muassa ×1, ×4, ×8 ja ×16 -väylille linjojen määrän mukaan. Pienemmällä liittimellä varustettuja laitteita voidaan liittää suurempaan liittimeen. Arkkitehtuurin ja signaloinnin puolesta suuremman väylän laite voitaisiin liittää myös pienempään väylään, sillä kytkettäessä laitteet säätävät nopeutensa käytössä olevien linjojen mukaan. Tosin useimmissa tapauksissa suuremmat liittimet eivät kuitenkaan ole fyysisesti yhteensopivia pienempien kanssa.[5]

Vanhempia PCI-väylää käyttäviä laajennuskortteja ei voi liittää PCIe-väylään eikä toisinpäin, sillä väylät ovat täysin erilaisia eivätkä millään tasolla yhteensopivia tai samankaltaisia nimeään ja käyttötarkoitustaan lukuun ottamatta.[42]

Sovellukset ja käyttökohteet

[muokkaa | muokkaa wikitekstiä]| Tähän artikkeliin tai osioon ei ole merkitty lähteitä, joten tiedot kannattaa tarkistaa muista tietolähteistä. Voit auttaa Wikipediaa lisäämällä artikkeliin tarkistettavissa olevia lähteitä ja merkitsemällä ne ohjeen mukaan. |

Ensimmäisenä vanhoista väyläratkaisuista PCIe:hen ovat siirtyneet suuria tiedonsiirtonopeuksia tarvitsevat laitteet kuten esimerkiksi tehokkaat näytönohjaimet, verkkokortit ja kiintolevyohjaimet. Nykyään myös muita oheislaitteita on yhä enemmän tarjolla PCIe -liitännällä, esimerkkinä suurinopeuksiset SSD-levyt (M.2-liitäntä).

Muita käyttökohteita ovat koneoppimiseen ja tekoälyyn suunnatut kiihdyttimet.[43]

Katso myös

[muokkaa | muokkaa wikitekstiä]Lähteet

[muokkaa | muokkaa wikitekstiä]- ↑ a b Zhang, Yanmin & Nguyen, T. Long: Enable PCI Express Advanced Error Reporting in the Kernel (PDF) Proceedings of the Linux Symposium. kesäkuu 2007. Fedora project. Viitattu 11.3.2014. (englanniksi)

- ↑ Teglet, Traian: AGP Almost at the End of the Road 5.6.2008. Softpedia. Viitattu 16.3.2014. (englanniksi)

- ↑ a b Wilson, Trasy V.: How PCI Express Works HowStuffWorks. Viitattu 16.3.2014. (englanniksi)

- ↑ PCIe® Base 3.1 Specification, PCIe Card Electromechanical 3.0 Specification PCI-SIG. Viitattu 8.3.2015. (englanniksi)

- ↑ a b c d e f g Torres, Gabriel & Lima, Cássio: Everything You Need to Know About the PCI Express 12.7.2012. Hardware Secrets. Arkistoitu Viitattu 11.3.2014. (englanniksi)

- ↑ Bhatt, Ajay V.: Creating a PCI Express Interconnect (PDF) PCI-SIG. Viitattu 18.3.2014. (englanniksi)

- ↑ https://www.onlogic.com/company/io-hub/pcie-5-0/

- ↑ https://www.bestgamingreviews.com/how-many-pcie-lanes-does-m-2-slot-use/

- ↑ https://www.gamersnexus.net/news-pc/3611-amd-a520-chipset-comparison-specs

- ↑ https://www.anandtech.com/show/15999/amd-releases-the-a520-chipset-for-ryzen-3000-on-a-budget

- ↑ a b PCI-SIG Engineering Change Notice (PDF) 16.3.2006. PCI-SIG. Viitattu 18.3.2014. (englanniksi)

- ↑ About ExpressCard Technology USB Implementers Forum, Inc. Viitattu 18.3.2014. (englanniksi)

- ↑ Chris Loberg: Get ready for M-PCIe testing 25.10.2013. The EDN Network. Viitattu 11.3.2014. (englanniksi)

- ↑ a b Myslewski, Rik: The future of PCIe: Get small, speed up, think outside the box 13.9.2013. The Register. Viitattu 4.3.2014. (englanniksi)

- ↑ 22 Industry Leaders Join Arapahoe Work Group as Key Developers 29.8.2001. PCI-SIG. Viitattu 16.3.2014. (englanniksi)

- ↑ PCI Express 4.0 Frequently Asked Questions PCI-SIG. Viitattu 9.9.2014.

- ↑ a b PCI Express 3.0 Frequently Asked Questions PCI-SIG. Viitattu 16.3.2014.

- ↑ a b c d e Ryan Smith: PCI Express 6.0 Specification Finalized: x16 Slots to Reach 128GBps anandtech.com. 11.1.2022. Viitattu 30.10.2022. (englanniksi)

- ↑ a b c d e f g h Rowe, Martin: What does GT/s mean, anyway? 1.3.2007. EDN. Viitattu 11.3.2014. (englanniksi)

- ↑ PCI-SIG® Presents: PCI Express™ 1.1 & PCI Firmware 3.0 Technical Update 25.2.2005. PCI-SIG. Viitattu 4.3.2014. (englanniksi)

- ↑ PCI-SIG delivers PCI Express 2.0 specification (PDF) 15.1.2007. PCI-SIG. Viitattu 11.3.2014. (englanniksi)

- ↑ Smith, Tony: PCI Express 2.0 final draft spec published 11.10.2006. The Register. Viitattu 16.3.2014. (englanniksi)

- ↑ Key, Gary & Fink, Wesley: Intel P35: Intel's Mainstream Chipset Grows Up 21.5.2007. AnandTech. Viitattu 16.3.2014. (englanniksi)

- ↑ Huynh, Anh Tuan: NVIDIA "MCP72" Details Unveiled 7.6.2009. DailyTech. Viitattu 16.3.2014. (englanniksi)

- ↑ Intel P35 Express Chipset Product Brief (PDF) Intel. Viitattu 16.3.2014. (englanniksi)

- ↑ Difference Between PCI 2.0 and PCI 2.1 11.5.2011. DifferenceBetween.net. Viitattu 16.3.2014. (englanniksi)

- ↑ Hachman, Mark: PCI Express 3.0 Spec Pushed Out to 2010 5.8.2009. PCMag.com. Viitattu 16.3.2014. (englanniksi)

- ↑ PCI Express 3.0 Bandwidth: 8.0 Gigatransfers/s 9.8.2007. ExtremeTech. Viitattu 16.3.2013. (englanniksi)

- ↑ Shilov, Anton: PCI Special Interest Group Publishes PCI Express 3.0 Standard 18.11.2010. X-bit labs. Viitattu 16.3.2014. (englanniksi)

- ↑ Martin, Ryan: PCIe 3.1 and 4.0 Specifications Revealed 1.7.2013. eTeknix. Viitattu 4.3.2014. (englanniksi)

- ↑ a b c d e What’s the Difference Going from PCIe 3.0 to PCIe 6.0? electronicdesign.com. 9.7.2020. Viitattu 6.1.2021. (englanniksi)

- ↑ PCI-SIG announces PCI Express 4.0 evolution to 16GT/s, twice the throughput of PCI Express 3.0 technology 29.11.2011. PCI-SIG. Viitattu 16.3.2014. (englanniksi)

- ↑ Suvanto, Ville: PCI-SIG paljasti PCI Express 4.0:n 29.11.2011. Muropaketti. Viitattu 19.3.2014.

- ↑ PCI Express 4.0 Frequently Asked Questions pcisig.com. PCI-SIG. Viitattu 8.3.2015. (englanniksi)

- ↑ Eric Born: PCIe 4.0 specification finally out with 16 GT/s on tap 8.6.2017. Tech Report. Viitattu 19.6.2019. (englanniksi)

- ↑ PCI Express 4.0 Frequently Asked Questions PCI-SIG. Viitattu 19.6.2014. (englanniksi)

- ↑ Paul Alcorn: PCIe 5.0 Is Ready For Prime Time 17.1.2019. Tom's Hardware. Viitattu 25.5.2019. (englanniksi)

- ↑ PCI-SIG Announces Upcoming PCI Express 6.0 Specification to Reach 64 GT/s 18.6.2019. Business Wire. Viitattu 19.6.2019. (englanniksi)

- ↑ The Tech Tricks That Make PCI-Express 6.0 And Beyond Possible nextplatform.com. 6.8.2020. Viitattu 10.8.2020. (englanniksi)

- ↑ PCI-SIG Releases PCIe 6.0 Specification Delivering Record Performance to Power Big Data Applications businesswire.com. 11.1.2022. Viitattu 11.1.2022. (englanniksi)

- ↑ Andrew Cunningham: PCI Express 7.0 standard provides eight times the bandwidth of today’s connections arstechnica.com. 23.6.2022. Viitattu 30.10.2022. (englanniksi)

- ↑ How can I tell the difference between PCI, PCI-X and PCI Express? We Love Macs. Viitattu 16.3.2014. (englanniksi)

- ↑ How PCIe Technology Enables Machine Learning and Artificial Intelligence pcisig.com. Viitattu 6.1.2021. (englanniksi)

Aiheesta muualla

[muokkaa | muokkaa wikitekstiä]- PCI-SIG (englanniksi)

- PCI Express Architecture, Intel Developer Network (englanniksi)

- How PCI Express works (englanniksi)